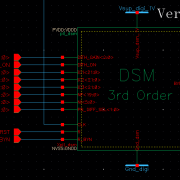

Featured Circuit #1: A High-Speed Delta-Sigma Modulator for a Fractional-N PLL

This is the first in an occasional series of news items showcasing some developed technology (i.e. internal intellectual property). To start the series is a Delta-Sigma Modulator for a Fractional-N PLL for generating carrier frequencies in the range of tens of Gigahertz. This has been proven in 2 designs on different process nodes so far.

The circuit is a 22-bit third-order MASH (‘Multi-stAge noise Shaping’) pipelined Delta-Sigma Modulator, in Verilog RTL. The design challenge here is reaching an input clock frequency of 600MHz or more.

There is selectable first-, second- or third-order derivatives of dithering, or the raw LFSR dither signal itself, or dithering can be disabled. Dither gain and initialisation MASH accumulator values as well as 6-bit integer and 20-bit fraction values are the other programmable parameters. The design includes Built-In Self-Test (BIST) hardware for at-speed testing.

One implementation was with a ‘vanilla’ (standard threshold voltage) library in a 130nm process. For the purposes of reporting comparable performance, the clean layout has timing closure at 746MHz slow corner, 125oC when with zero setup clock uncertainty and 0% OCV derating. Extra margin quickly brings this frequency down! Higher performance could have be achieved with manual intervention in layout because of the regular structure of the MASH which constitutes a significant proportion of the design but this has not been necessary so far.

An application example, also purely for illustrative purposes is as follows: given an integer value 12 and a fraction value of 345678, it will provide a delta-sigma sequence with average value 12+345678/2^20 = 12.32966423. Used within a Fractional-N PLL with a reference frequency of 500MHz, the PLL would then generate an output frequency of 6.164832GHz. A simple alternative to the Delta-Sigma modulator could generate a sequence of 12s and 13s such that the long-term average is 12.32966423 but this would be produce spurious tones in the PLL’s output. Instead, the MASH produces noise-shaped sequences (with values spread between 10 and 16) such that spurious noise is significantly reduced.